Что такое базовый процессор?

5/8/2023 10:57:48 AM

Процессор базовой полосы синтезирует сигналы базовой полосы, которые будут отправлены, и декодирует полученные сигналы базовой полосы. При отправке сигнала базовой полосы он компилирует звуковой сигнал в код базовой полосы; При получении сигнала он расшифровывает код базовой полосы как звуковой сигнал. В то же время процессор базовой полосы также отвечает за компиляцию адресной информации, текстовой информации, информации изображения и так далее.

Процессор базовой полосы представляет собой сложный интегрированный SOC. Основные процессоры базовой полосы поддерживают несколько сетевых стандартов, то есть все стандарты мобильных и беспроводных сетей, включая 2G, 3G, 4G и Wi - Fi, на одном процессоре базовой полосы. В настоящее время большинство базовых процессоров - это микропроцессоры и цифровые сигнальные процессоры. Микропроцессор является центром управления для всего чипа, большинство из которых использует ядро ARM, а подсистема DSP отвечает за обработку базовой полосы.

Процессор базовой полосы

Процессор базовой полосы в смартфоне можно понимать как сложный SoC - чип с несколькими функциями, каждая из которых настроена и скоординирована с помощью микропроцессора. Этот сложный чип, ориентированный на ARM - микропроцессор, управляет и настраивает каждый периферийный функциональный модуль вокруг ARM - микропроцессора через выделенную шину ARM - микропроцессора (AHB - шину), которая в основном включает GSM, WiFi, GPS, Bluetooth, DSP и память. Каждый функциональный модуль имеет свою собственную память и адресное пространство. Их функции независимы друг от друга. Сам процессор базовой полосы имеет чип управления питанием.

Компоненты процессоров базовой полосы II

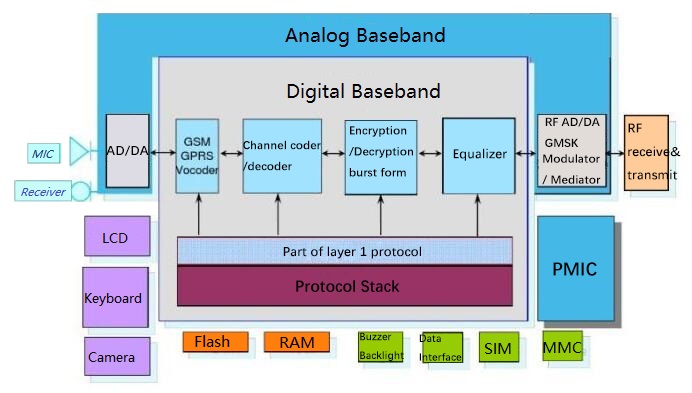

Процессор базовой полосы можно разделить на пять подсистем: процессор CPU, кодер канала, цифровой сигнальный процессор, модем и интерфейсный модуль.

Процессор CPU: управление и управление всей мобильной станцией, включая управление временем, управление цифровой системой, радиочастотное управление, управление энергосбережением, управление интерфейсом человека и машины. В случае использования скачкообразной перестройки частоты она также должна включать контроль скачкообразной перестройки частоты. В то же время процессор CPU выполняет все программные функции терминала GSM, а именно: первый уровень (физический уровень) протокола связи GSM, второй уровень (уровень передачи данных), первый уровень (сетевой уровень), человеко - машинный интерфейс (MMI) и программное обеспечение прикладного уровня.

Кодер каналов: кодирование и шифрование каналов, которые в основном выполняют бизнес и управляют информацией, включая сверточный код, код FIRE, код проверки чётности, переплетение, форматирование внезапных импульсов.

Процессор цифрового сигнала: в основном завершает выравнивание каналов на основе алгоритма Витби и кодирование речи на основе технологии долгосрочного прогнозирования импульсного возбуждения (RPE - LPC).

Модем: модуляция / демодуляция, необходимая для выполнения в основном гауссовой системы управления клавишами с минимальным сдвигом частоты (GMSK).

Модуль интерфейса: включает в себя три подсистемы: аналоговый интерфейс, цифровой интерфейс, интерфейс человека и машины.

Какие сетевые стандарты поддерживает мобильный терминал, определяются режимом процессора базовой полосы, а какие диапазоны частот поддерживаются антенной и радиочастотным модулем. Процессор базовой полосы выполняет функцию доступа к мобильному терминалу. Текущий процессор базовой полосы представляет собой очень сложную систему на экране (SoC), которая не только поддерживает различные стандарты связи (включая GSM, CDMA 1x, CDMA2000, WCDMA, HSPA, LTE и т. Д.), но и предоставляет мультимедийные функции и интерфейсы, связанные с мультимедийными дисплеями, датчиками изображения и аудиоустройствами. Чтобы еще больше упростить конструкцию, схемы управления питанием, необходимые для этих компиляционных схем, все чаще интегрируются в них.

Архитектура SOC процессора базовой полосы

Функции цифровой обработки базовой полосы и основные периферийные функции мобильного телефона сосредоточены в системе на чипе (SOC), базовая архитектура которой использует структуру микропроцессора + цифрового сигнального процессора (DSP), что повышает пропускную способность микропроцессоров и DSP.

Микропроцессор является центром управления для всего чипа и будет работать с встроенной операционной системой реального времени (например, Nucleus PLUS).

Подсистема DSP находится в центре внимания обработки базовой полосы и содержит множество аппаратных дросселей и специальных модулей обработки базовой полосы для выполнения всех функций физического слоя.

С развитием технологии цифровой обработки сигналов в реальном времени микропроцессоры ARM (которые будут использовать различные микросерии, а чипы 3G будут в основном использовать ARM9), архитектуры DSP и FPGA стали основными способами обработки базовой полосы мобильных терминалов.

Архитектура ARM процессора с базовой полосой

В области архитектуры чипов можно сказать, что X86 и ARM конкурируют десятилетиями и занимают непоколебимые позиции в своих областях. Среди них X86 доминирует на рынке чипов для ПК, а ARM доминирует на рынке чипов для мобильных терминалов. Благодаря низкой стоимости, энергопотреблению и высокой эффективности архитектуры ARM, она соответствует тенденциям развития многих мобильных терминалов, включая смартфоны.

На рисунке ниже показана логическая архитектура типичного процессора базовой полосы на основе ARM, в котором логика базовой полосы 3G / 4G относится к вычислительной подсистеме DSP.

Микропроцессор выполняет многозадачное планирование, межзадачную связь, периферийные драйверы и связь между микропроцессором и подсистемой DSP и другими модулями через операционную систему реального времени RTOS (например, Nucleus PLUS).

Функции также включают:

(1) управление и управление всей мобильной станцией, включая управление временем, управление цифровой системой, радиочастотное управление, управление энергосбережением и так далее;

(2) Выполнение всех программных функций, то есть связь между физическим уровнем протокола беспроводной связи и стеком протокола, расширенным стеком протокола (TCP / IP и т. Д.), также будет включать интерфейс взаимодействия человека и машины (MMI) и приложения, если они используются в функциональной машине.

2 подсистема DSP используется для обработки всех алгоритмов на физическом уровне, включая кодирование каналов, шифрование, выравнивание каналов, кодирование речи, модуляцию и демодуляцию. Средства передачи данных между подсистемой DSP и подсистемой микропроцессора включают двухпортовую память с произвольным доступом (RAM), Многошинные общие ресурсы (некоторые поставщики используют многослойные шинные протоколы AMBA) и т. Д. Многомодовые многочастотные базовые процессоры могут содержать несколько DSP.

3 Что касается организации памяти, то как микропроцессоры, так и подсистемы DSP могут иметь свой собственный кэш с общим SRAM на чипе и общей внешней расширенной памятью. Расширенная память обычно поддерживает синхронную динамическую случайную память (SDRAM) и флэш - память типа NAND.

FLASH ROM может использоваться для хранения загрузочных ROM и CP ROM для подключения операционных систем и пользовательских приложений. Интерфейс ROM в основном используется для подключения FLASH ROM к программе хранения данных, а интерфейс RAM в основном используется для хранения статических RAM (SRAM) временных данных. Встроенная в пластину статическая память с произвольным доступом большой емкости (SRAM) стала очень распространенной, что способствует снижению энергопотребления и снижению системных затрат.

4 Что касается периферийных устройств и интерфейсов, процессоры базовой полосы обычно поддерживают несколько интерфейсов для облегчения связи с процессорами приложений и добавляют другие модули, такие как WiFi и GPS. Интерфейсы включают UART, мультимедийный интерфейс (MMI), универсальную последовательную шину (USB), SPI и так далее.

Связь между MCU и внешним интерфейсом может быть выполнена с помощью DMA, и если процессор базовой полосы не интегрирован с RF, он также имеет специальный RF - интерфейс

ВЫВОДЫ

Обычно мы думаем, что производительность процессора мобильного телефона отражается в его скорости обработки и энергопотреблении. На самом деле, в эпоху смартфонов существует слой самых основных и критических потребностей - качество сигнала мобильного телефона. Эта функция связи, определяемая процессором базовой полосы, будет напрямую влиять на качество звонков и скорость сети.

С появлением сетей 5G и телефонов 5G быстрый захват доли на рынке процессоров с базовой полосой 5G поможет гигантам чипов увеличить свои финансовые доходы, тем самым опережая и формируя добродетельный цикл в сетях 6G.

Russia

Russia

English

English 简体中文

简体中文 Russia

Russia

2023-05-08

2023-05-08